Flache Baugruppen wie elektronische Leiterplatten können aufgrund ihrer meist großflächigen Probengeometrie in nur unzureichend guter Auflösung untersucht werden. Der Abstand zwischen Röntgenquelle und Probe ist meist zu groß, um kleine Teilbereiche genauer zu untersuchen und kleinste Fehler wie Risse oder Poren in Lötverbindungen (BGA, QFN, QFP) zu detektieren.

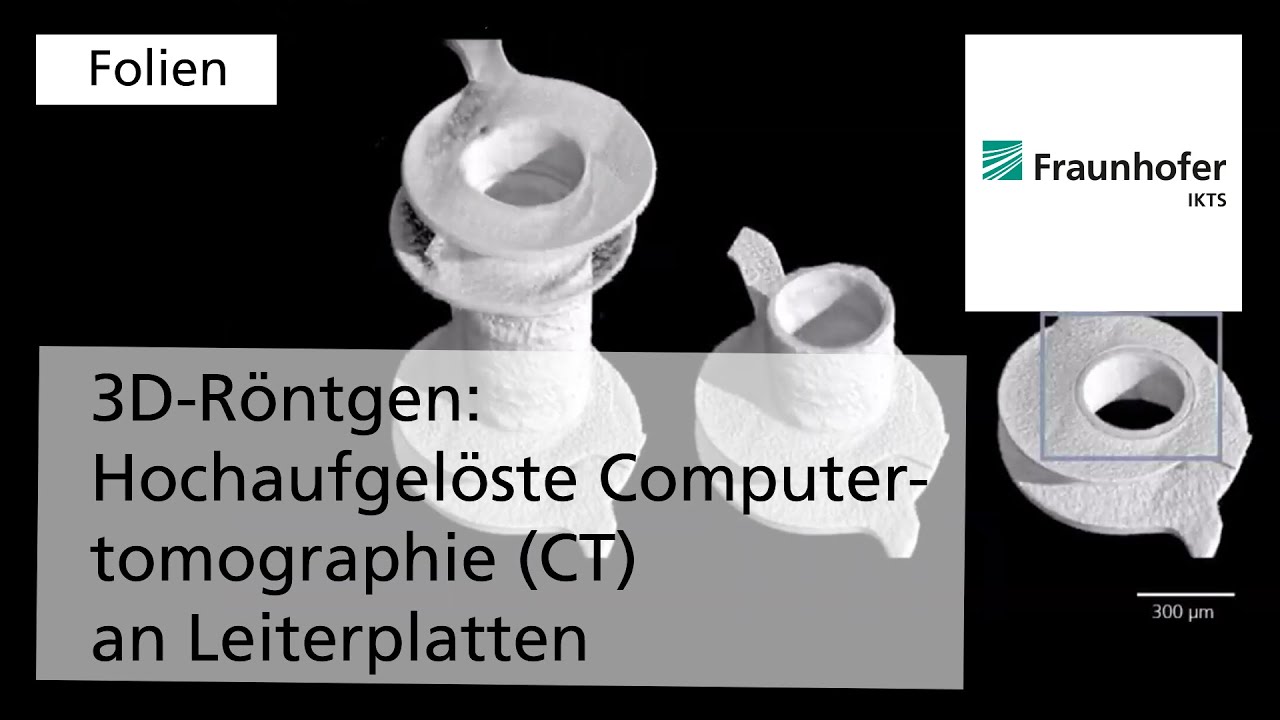

Das Fraunhofer IKTS bietet für diese Aufgabenstellung ein spezielles Röntgen-Tomographieverfahren an, das Teilbereiche großflächiger Schaltungsträger wie Leiterplatten hochaufgelöst und zerstörungsfrei analysieren kann.